http://ojs.bbwpublisher.com/index.php/JERA

ISSN Online: 2208-3510 ISSN Print: 2208-3502

## Design of a Technology Verification Platform for Space Electromagnetic Interference Signal Testing and Analysis

Qi Liu\*, Huiwen Du, Chao Zhang, Yazhou Zhang

China Electronics Technology Ceyear Technology Co., Ltd., Qingdao 266555, Shandong Province, China

\*Corresponding author: Qi Liu, liuqi149@ceyear.com

**Copyright:** © 2024 Author(s). This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY 4.0), permitting distribution and reproduction in any medium, provided the original work is cited.

**Abstract:** This paper designs a space electromagnetic interference signal test and analysis technology verification platform. The article firstly introduces the general scheme of the technical verification platform and then describes each component unit of the hardware and the overall structure of the software in detail. The platform can achieve a 10 MHz ~ 50 GHz working frequency band, 1.2 GHz acquisition and real-time recording bandwidth, 6 GB/s recording rate, and 12 TB recording capacity.

Keywords: Real-time recording bandwidth; Recording rate; Recording capacity; Playback analysis

Online publication: September 30, 2024

#### 1. Introduction

With the wide application of software radio technology, complex electromagnetic interference signal testing technology is developing rapidly [1]. In the field of testing, the amount of information contained in electromagnetic signals is increasing, and various broadband, complex, fast-changing, and difficult-to-reproduce electromagnetic interference signals emerge in endlessly, and a lot of valuable information is often hidden in huge useless information or interference signals. This then puts forward an urgent new demand for wideband radio frequency signal acquisition, storage, and playback analysis [2].

In this paper, a verification platform for space electromagnetic interference signal testing and analysis technology is designed. The platform has complete on-site acquisition, long-term storage, post-event playback analysis, and other test methods. This can solve the problems of space electromagnetic signal monitoring and recording, electromagnetic interference search and analysis, electromagnetic environment simulation and reconstruction, signal processing algorithm simulation and verification in the fields of navigation, radar, meteorology, aerospace, communications, and electromagnetic information security, among other things.

## 2. Overall design

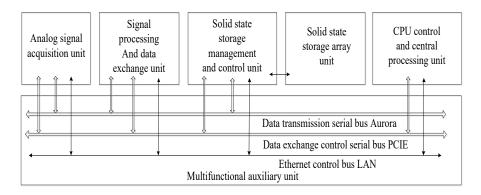

The space electromagnetic interference signal test and analysis technology verification platform is mainly composed of an analog signal acquisition unit, signal processing, data exchange unit, solid-state storage management and control unit, solid-state storage array unit, central processing unit (CPU) control and central processing unit, backplane, power supply, and human. The multi-functional auxiliary unit comprises a computer-computer interaction module, composed of six units. The schematic block diagram of the overall hardware scheme is shown in **Figure 1**.

Figure 1. Hardware overall design schematic diagram

This platform can not only complete the reception and acquisition of microwave signals and long-term seamless recording but also complete the playback and analysis of recorded signals <sup>[3]</sup>. In the recording mode, the entire platform can complete the mass storage of collected data. The stored data stream adopts the format of data packets. In addition to the stored data, it also contains information such as the center frequency and bandwidth set by the user. On the other hand, the stored data can be continuously played back to the signal processing and signal analysis unit, and the playback analysis of the stored data can be completed through the pre-analysis of the high-speed signal processing unit or the offline in-depth analysis software of the host.

## 3. Hardware design

### 3.1. Analog signal acquisition unit

The analog signal acquisition unit completes the conditioning and high-speed acquisition of intermediate frequency signals, realizes the conversion from analog signals to digital signals, completes digital down-conversion of digital signals, frequency response correction compensation, realizes preprocessing of digital signals, and realizes start-stop and timing control for acquisition, and storage and digital signal processing.

#### 3.2. Signal processing and data exchange unit scheme

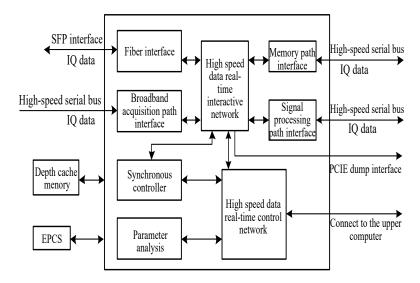

The high-speed signal processing and data exchange unit includes two functional parts of high-speed data real-time interaction and signal processing and analysis. The high-speed data real-time interaction module is the data interaction hub of the entire platform, which is responsible for the real-time interaction of high-speed data, parameters, and control information among broadband acquisition channels, optical fiber interface channels, signal processing channels, storage channels, and dump channels. A high-speed data real-time interaction module block is shown in **Figure 2**.

Figure 2. High-speed data real-time interaction module block diagram

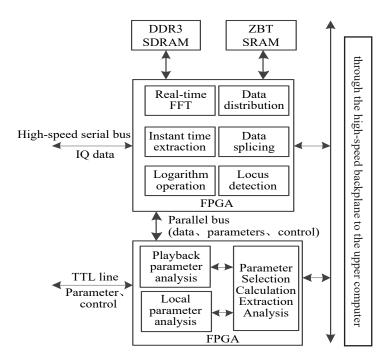

The signal processing and analysis module is used to realize real-time processing of digital signals and various signal analysis functions and is mainly used as a quick preview of signals. Its data source can be either online test data collected by the front end or recorded data, that is, the hardware unit can realize online and offline signal processing and signal analysis to achieve online real-time monitoring function and offline analysis hardware acceleration function. The block diagram of the signal processing and analysis module is shown in **Figure 3**.

**Figure 3.** The signal processing and analysis module diagram

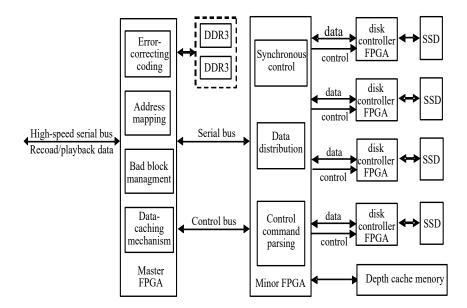

# 3.3. Solid-state storage management and control unit and solid-state storage array unit scheme

The large-capacity solid-state storage and control unit mainly completes high-speed and large-capacity data recording, playback, task management, and file management. The block diagram of its scheme is shown in **Figure 4**.

Figure 4. Solid-state storage management and control unit and solid-state storage array diagram

In the high-speed and large-capacity solid-state storage unit, the main control Field-Programmable Gate Array (FPGA), Double Data Rate 3 (DDR3) cache array, and other devices are responsible for the interaction of data and control information, command analysis and data file management, and the auxiliary control FPGA is used to realize data distribution. The main control FPGA receives and analyzes the control commands sent to it, handling disk control management and directory management of the storage board. This includes tasks such as file querying, address mapping, implementation of the wear-leveling algorithm, Flash bad block management, and fragment recovery, among others. Simultaneously, the managed file information is stored in Flash. The DDR3 buffer is responsible for the temporary cache of data. The high-speed and large-capacity solid-state storage unit is interconnected with the high-speed data real-time interaction unit through a special FPGA and 8-way high-speed serial bus to complete the recording and playback functions.

#### 3.4. CPU control and central processing unit scheme

The whole machine control and playback analysis unit primarily consists of a high-performance embedded computer. The CPU of the embedded computer is an Intel Core i7 processor, and it features 8 GB of DDR3 memory. This unit handles platform hardware control, offline analysis, and other functions.

#### 3.5. Multifunctional auxiliary unit scheme

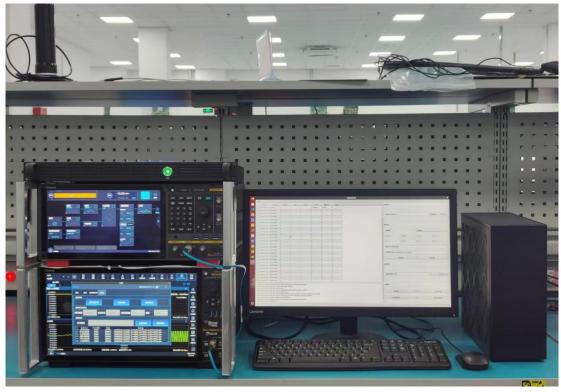

The multifunctional auxiliary unit mainly includes a power supply module, a fan assembly, a clock module, and a human-computer interaction module. The power supply module provides the required power for other units, the fan assembly provides air-cooling and heat dissipation for each module in the chassis, and the clock module provides a high-precision sampling clock for Analog-to-Digital Converter (ADC) and the working clock of other devices [4]. Concurrently, this platform has the real-time monitoring function of a waterfall diagram and has multiple analysis functions including pulse analysis, demodulation analysis, and digital modulation identification. The validation platform is shown in **Figure 5**.

Figure 5. The validation platform

## 4. Software design

In this paper, a multi-threaded control system based on a multi-core processor is constructed, and the design concept of modularization, componentization, and hierarchy is adopted to design the acquisition, storage, and playback control software. The software adopts a distributed control system, mainly including the main control module and the massive data storage and management module.

The main control software carries out signal reception, acquisition, general testing, and online analysis functions, which not only needs to control the slow speed control of the receiving front-end, but also needs to control the high-speed transmission and digital processing of the digital part, and must also fully meet the needs of users' usage habits and data resource sharing. To this end, the mainstream Wintel architecture of the test instrument industry is used to build the main control environment, the Intel multi-core processor is used as the main controller, the Windows multi-task operating system is selected, and the Qt cross-platform tool is used for software design and development management, to meet the needs of platform software componentization and hierarchical design and development. The multi-core and multi-threaded architecture is adopted, which can not only meet the flexibility of various analysis functions but also meet the real-time and efficiency requirements of high-speed acquisition, processing, recording, and storage of broadband signals.

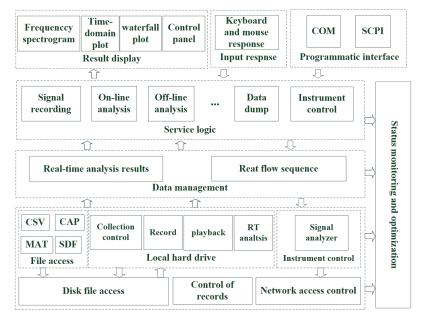

To reduce the complexity of software design, the software is divided into a plurality of functional modules, each functional module exists in the form of a dynamic link library, and carries out hierarchical design, mainly including user interaction (input response, result display, and programming interface), business logic (various functions and system calibration), data management (In-phase and Quadrature (I/Q) data and test process control sequence) and control interface (record control, file access, remote instrument control) four levels. Each layer includes a plurality of functional modules and can be subdivided into a plurality of functional components. The block diagram of the software scheme is shown in **Figure 6**.

Figure 6. Acquisition, storage, and playback control software block diagram

The user interaction layer is mainly composed of data graphical support components, program-controlled interface components, and offline playback analysis software components, which realize the interaction with users and external systems and interact with other levels of software through normalized interface components.

The business logic layer provides all the execution units and their operation interfaces required for the realization of the whole machine, including signal recording, online analysis, data dumping, offline analysis, and other functions. Among them, the offline analysis function is the call interface, which is used to call an independent offline analysis software based on the record file, and the recorded data is secondary analyzed, and the key information of the search is extracted and stored as a search index table, which is convenient for the rapid search or screening of signals.

The data management layer dynamically loads and configures the corresponding data receiving and processing components, record management and control components according to the parameter changes transmitted by the functional layer, and realizes test process control, data transmission and processing, and data record storage control.

The control interface layer completes the control of each hardware function module in the platform through the mapping signal acquisition, processing and recording components, the recording management and control components, and various drivers, control the hardware state change according to the timing set by the decomposition execution layer, receives and analyzes the data, records and stores the data. The interface is shown in **Figure 7**.

Figure 7. Software interface

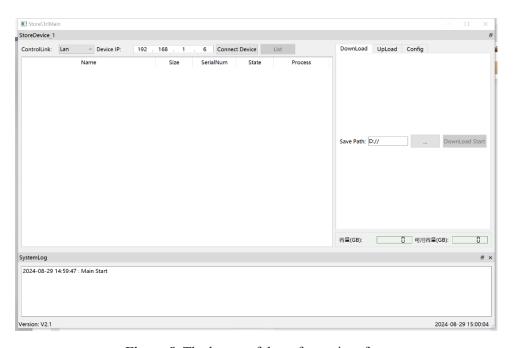

To facilitate the flexible management of recorded data, this paper also designs an independent massive signal data management function software that can be called by the main analyzer and provides three management options: status monitoring, file management, and advanced management. In status monitoring, it can provide status information such as the current working status and record the capacity usage. For example, users can select files based on parameters such as task number, task name, task size, start time, end time, center frequency, signal bandwidth, etc., and then delete, sort, or dump the selected files. In advanced management, it mainly includes user management and register query, in which the user management window mainly includes adding, deleting, modifying, and emptying user accounts, and the register query window is mainly used for debugging and maintenance. The layout of the software interface is roughly shown in **Figure 8**.

Figure 8. The layout of the software interface

#### 5. Conclusion

This paper designs a general microwave signal acquisition record and playback analysis system. The platform has the functions of real-time capture of electromagnetic signals, long-term seamless acquisition and massive data recording, and playback analysis functions such as massive recorded waveform observation and dynamic spectrum analysis. It can realize the working frequency band of  $10 \text{ MHz} \sim 50 \text{ GHz}$ , the acquisition and real-time recording bandwidth of 1.2 GHz, the recording rate of 6 GB/s, and the recording capacity of 12 TB.

## **Funding**

This work is supported by the China Electronics Technology Innovation Fund Project (Project No. KJ2202008).

#### Disclosure statement

The authors declare no conflict of interest.

#### References

- [1] Luo Y, Qin Y, 2022, Design of Intermediate Frequency (IF) Broadband Signal Acquisition, Storage and Playback System. Science Technology and Engineering, 22(10): 3998–4004.

- [2] Qian H, Li X, Yang W, et al., 2020, Design and Implementation of a Localized ADC/DAC Universal Test Platform Based on Labview and FPGA. Automation Technology and Applications, 39(6): 15–18, 53.

- [3] Meng Q, Du H, Zhan Y, et al., 2015, Design of Microwave Signal Sampling Recording and Playback Analysis System. 2015 National Conference on Microwave and Millimeter Wave Collected Papers.

- [4] Ding H, Zhang H, Pang J, 2021, FPGA-Based Design of High-Speed Large-Capacity Data Cache Unit. Instrumentation Technology and Sensors, 2021(6): 58–61.

- [5] Fan H, Wu X, Sun W, 2020, Design of a Radio Frequency Digital Integrated Broadband Transceiver Module. Radar Science and Technology, 18(3): 340–344, 350.

#### Publisher's note

Bio-Byword Scientific Publishing remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.