# Analysis of the Application of Low-Frequency Inter-Harmonic Monitoring in DC Converter Stations Based on Power Quality Monitoring Devices

Rui Xia\*

CYG Contron Co., Ltd., Zhuhai 519085, China

\*Author to whom correspondence should be addressed.

**Copyright:** © 2025 Author(s). This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY 4.0), permitting distribution and reproduction in any medium, provided the original work is cited.

**Abstract:** This article introduces an application case of monitoring low-frequency inter-harmonic signals in a DC converter station project using power quality monitoring devices, effectively providing data support for the sub-synchronous oscillation problems caused by the high-voltage DC system.

**Keywords:** Low frequency harmonic; Damping controller; Sub-synchronous oscillation

**Online publication:** December 31, 2025

## 1. Introduction

China leads the world in both the highest voltage levels and the largest number of operational DC transmission projects. With the widespread deployment of these projects, sub-synchronous oscillations caused by DC transmission have become a recurring issue. Notable cases include the Suizhong Power Plant, Yimin Power Plant, and Panan Power Plant, where such oscillations have threatened the longevity and safety of generator sets' shaft systems<sup>[1]</sup>. These oscillations arise from dynamic coupling and energy exchange between mechanical and electrical components in power systems, typically manifesting at low-frequency bands. Effective monitoring and early warning of DC system operations, supported by data, are crucial for identifying and addressing sub-synchronous oscillations. Using a specific DC transmission project as an example, this paper presents a low-frequency harmonic monitoring solution implemented through upgrades to power quality monitoring devices.

## 2. Analysis of sub-synchronous oscillation event in a DC transmission project

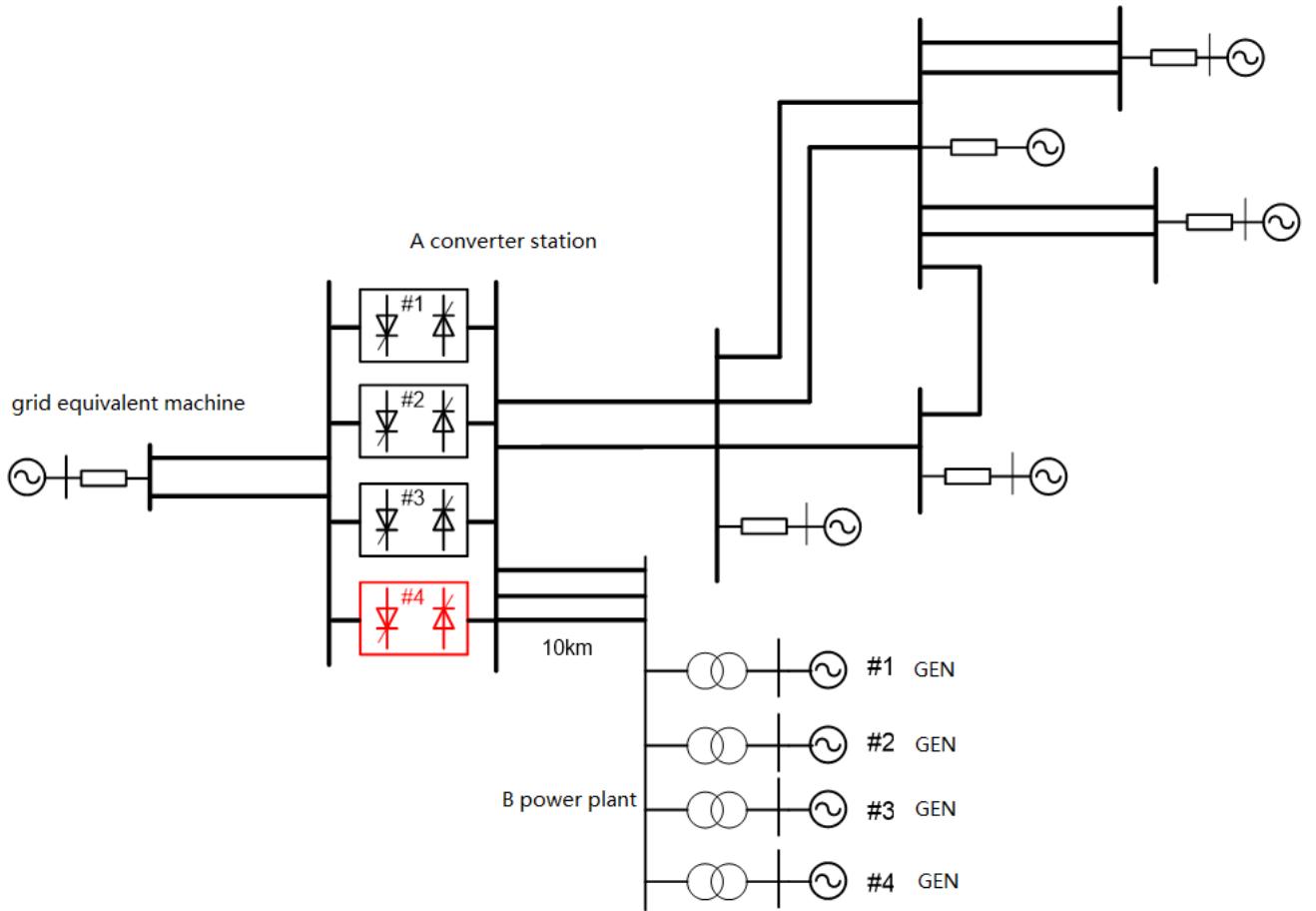

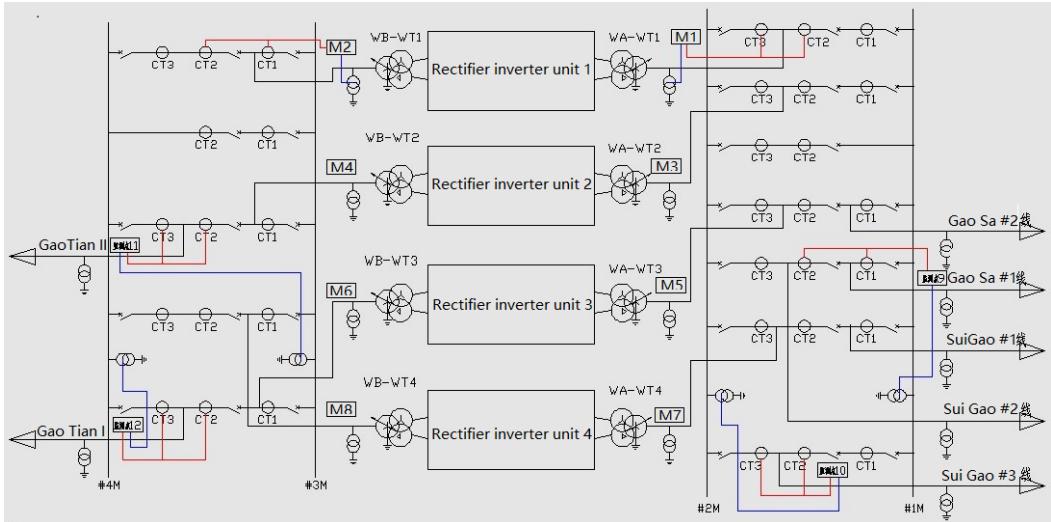

The first phase of a DC power project has completed four DC converter units (each rated at 750 MW), as shown in **Figure 1**. Power Plant B, located approximately 10 km from Converter Station A, has commissioned four generating units (#1, #2, #3, #4) that deliver power to Station A via three 500 kV transmission lines.

**Figure 1.** Schematic diagram of a DC transmission project.

During the incident, a random interval-triggered pulse anomaly with delayed response occurred in a bridge arm of Unit 4 at Converter Station A during continuous power frequency cycles, causing periodic interference to the AC system. Given that Power Plant B and Converter Station A are only 10 km apart and interconnected via three 500 kV AC transmission lines, the sub-synchronous frequency component in this interference became an excitation source for the power plant's units. This triggered modal oscillations with frequencies close to the shaft system's natural frequency, resulting in significant amplitude and prolonged duration of the oscillations.

At the same time, the additional sub-synchronous oscillation damping controller in the DC system of A converter station did not produce event records during the sub-synchronous oscillation, and the input and output waveform data of this module were also missing in the field data, so it was impossible to determine whether it played a damping control role.

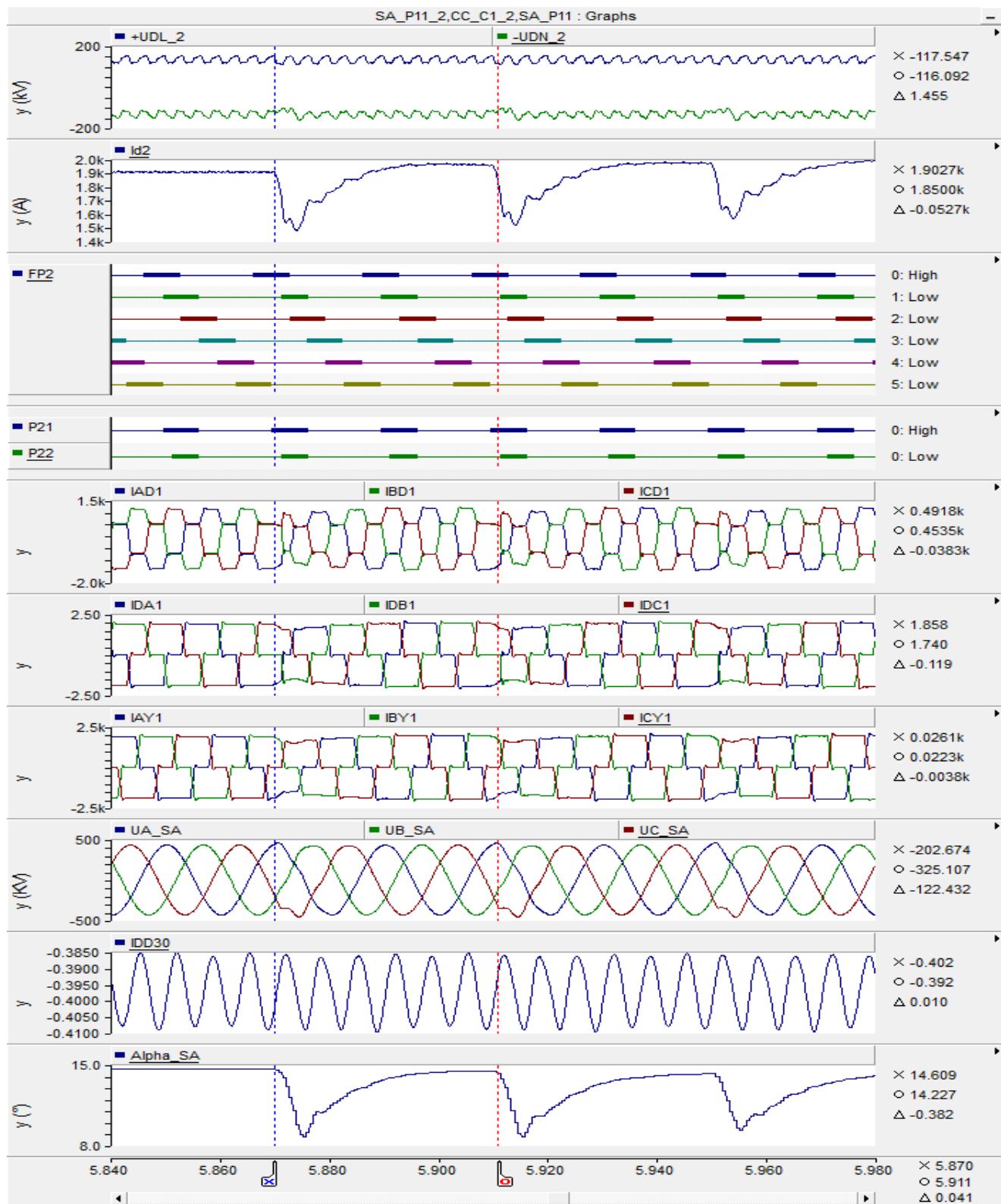

The EMTDC simulation was conducted, with valve 2 triggering delay occurring every two power frequency cycles. Unit 4 delivered 500 MW positive power, while the B-side D bridge's valve 2 triggered a 40 ms pulse interval, generating a 1.667 ms delay pulse. The simulation waveform is shown in **Figure 2**.

**Figure 2.** Simulation waveform diagram.

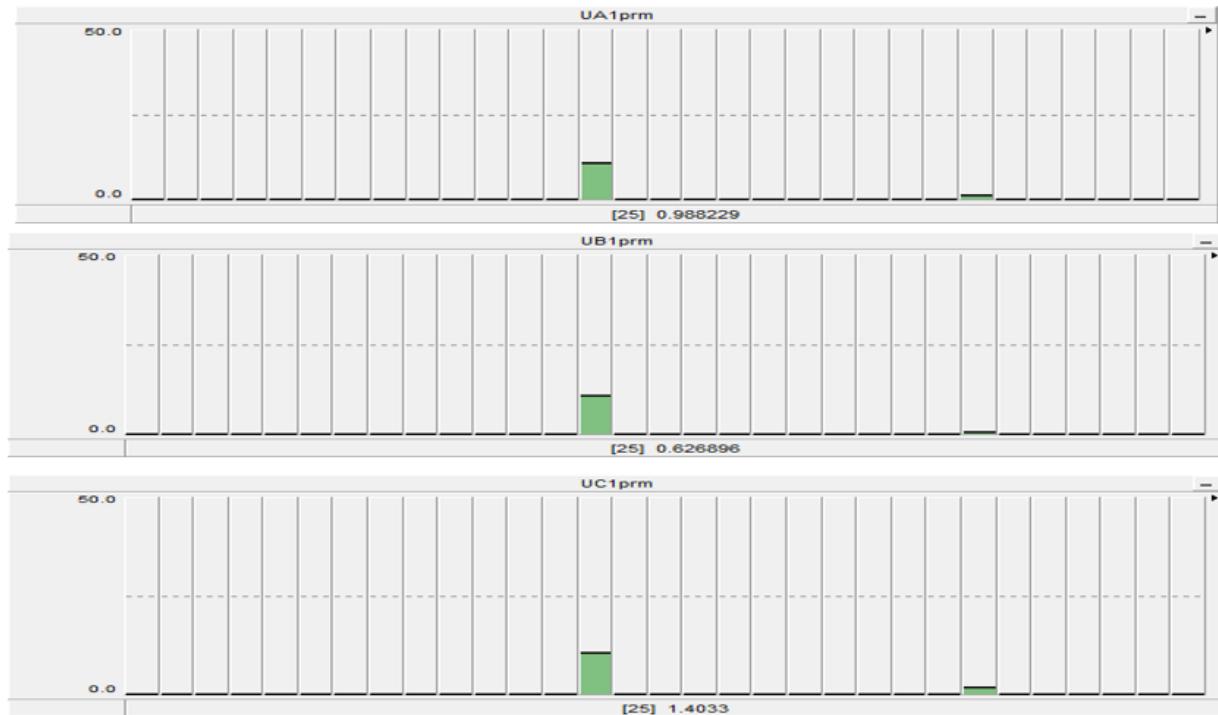

The simulation results demonstrate that a single-valve trigger with a one-cycle delay generates a 25 Hz sub-synchronous component in the DC system, which is also reflected in the AC voltage of the converter bus. **Figure 3** compares simulations with normal triggering and one-cycle delayed triggering, showing the 25 Hz component extracted from the converter bus voltage, with the C-phase voltage increasing from 0.0045 kV to 1.4033 kV.

**Figure 3.** Three synchronization component diagram.

Simulation results demonstrate that the disturbance originates from intermittent triggering lags of a single converter valve, rather than the sub-synchronous resonance-induced suppression function of the converter. As the damping controller failed to initiate alarm recording during the event, comprehensive data analysis of the disturbance process can be achieved through low-frequency harmonic data acquisition and parameter configuration of the damping controller.

### 3. Principle and parameter configuration of damping controller

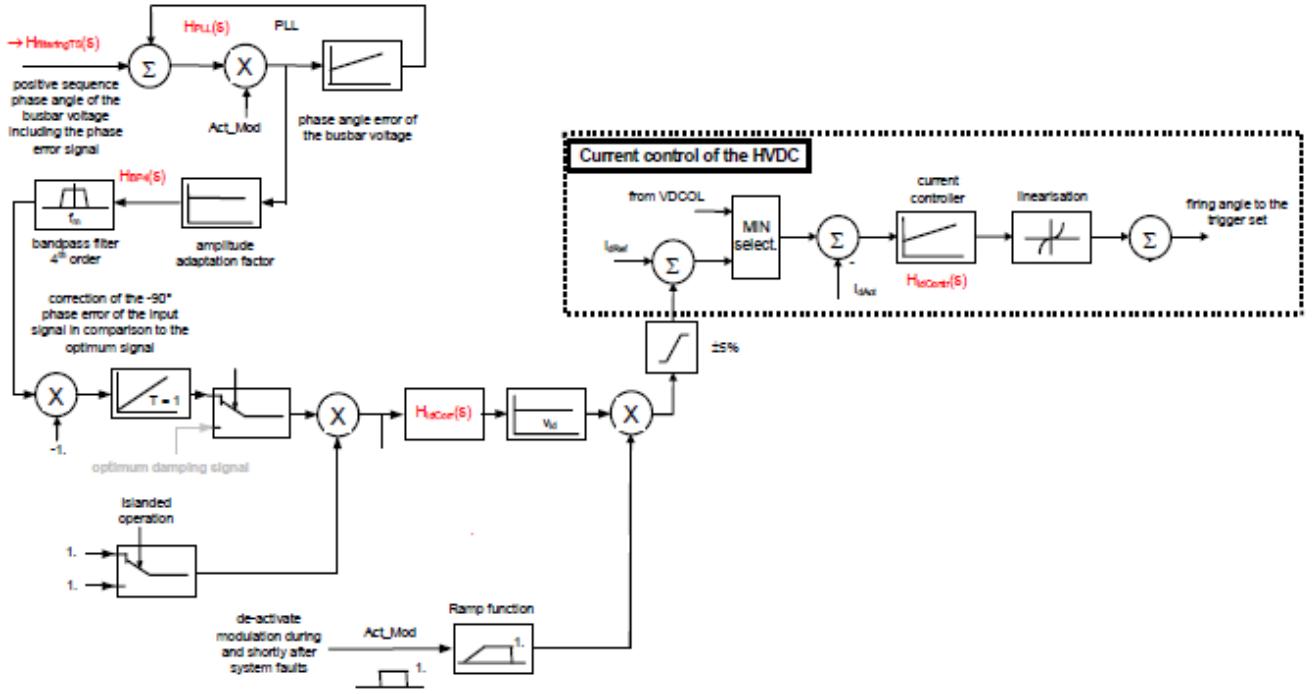

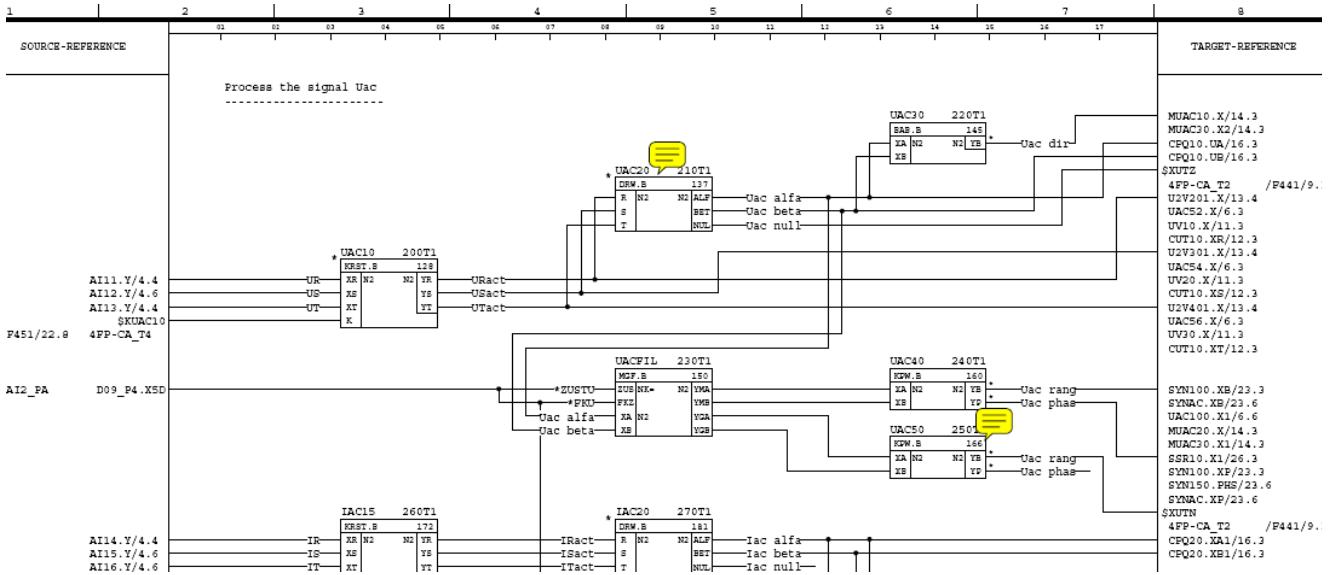

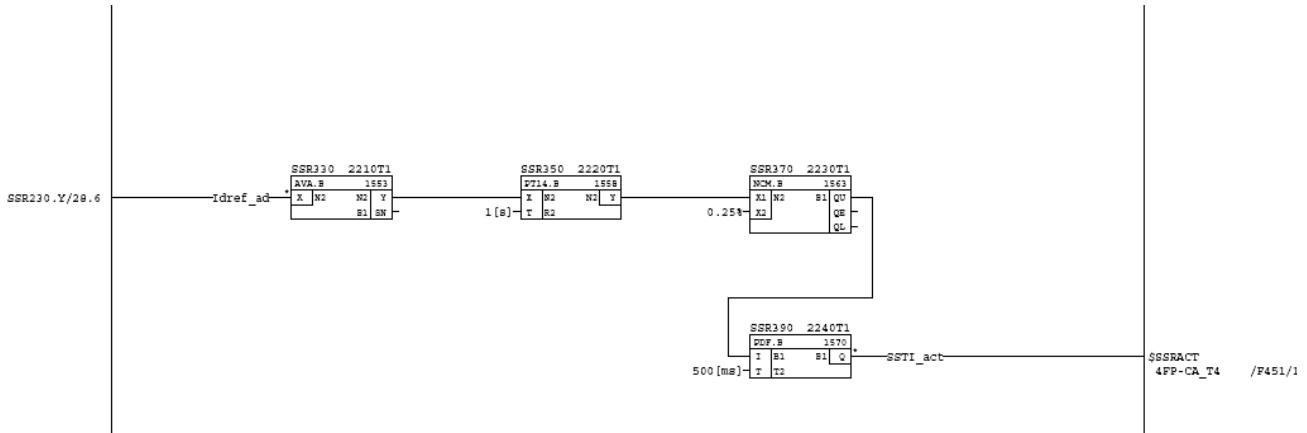

The measurement principle of the SSR in the pole control system of converter station A is illustrated in **Figure 4**.

Figure 4. SSR measurement principle diagram of the pole control system.

The damping controller operates by taking the phase angle of an AC voltage signal as input and generating a current modulation signal. Through real-time detection of phase angle variations, it dynamically adjusts the DC system's output power, thereby modifying the generator's electromagnetic torque. This mechanism maintains a positive damping coefficient for the generator within the 10 Hz to 30 Hz frequency range, effectively suppressing oscillations [2]. The phase relationship between the control signal and the resonant signal is critical to damping effectiveness. If the phases are out of sync, oscillations may not only fail to be suppressed but could even be exacerbated. To optimize damping performance, the controller must apply phase correction to the input signal using an appropriate transfer function.

### 3.1. Components of the damping controller

#### 3.1.1. Signal sampling process

The damping sub-synchronous oscillation function of Power Plant B measures the input voltage of the converter transformer. The measured input voltage undergoes  $\alpha\beta$  transformation to obtain the instantaneous value of the AC voltage, which is then used for the synchronization locking process. The sampling part of the program is shown in Figure 5.

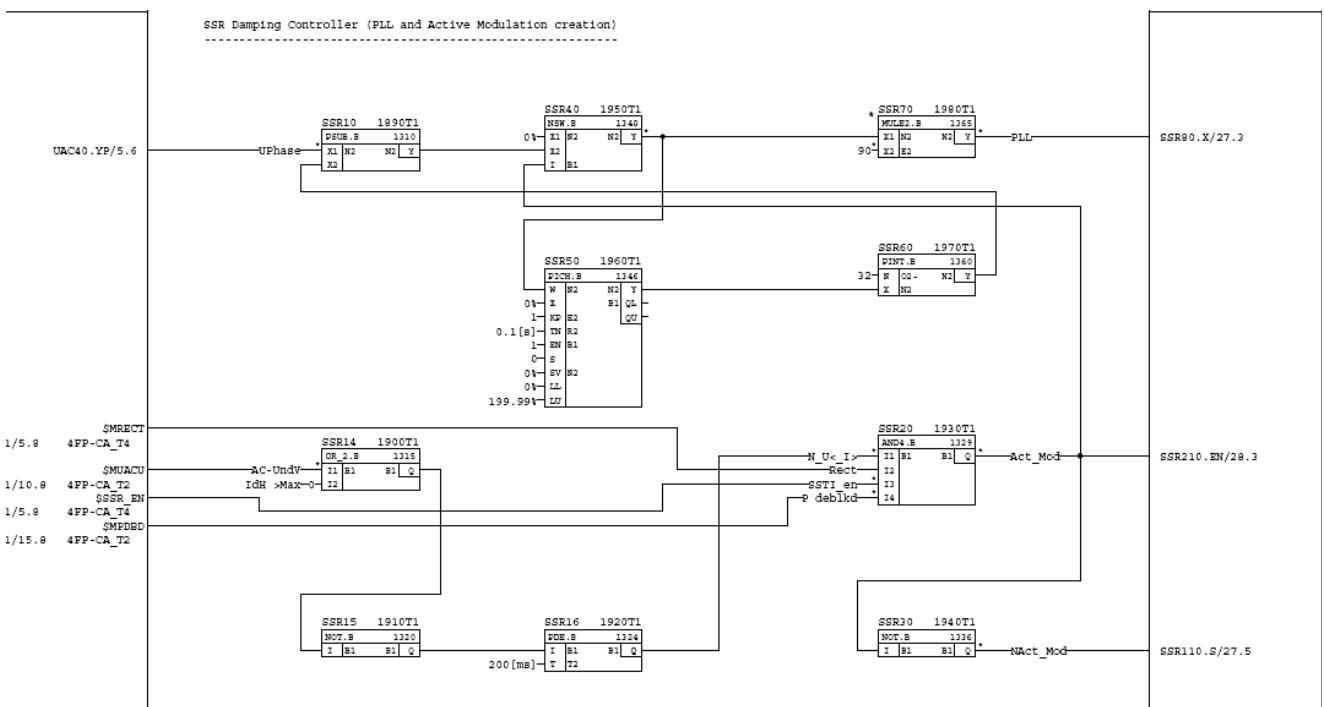

### 3.1.2. Phase-locking loop

The PLL circuit employs a PI controller with a gain of 1 and a time constant of 100 ms. The phase-locked loop (PLL) program is illustrated in Figure 6.

Figure 6. Block diagram of phase-locked loop.

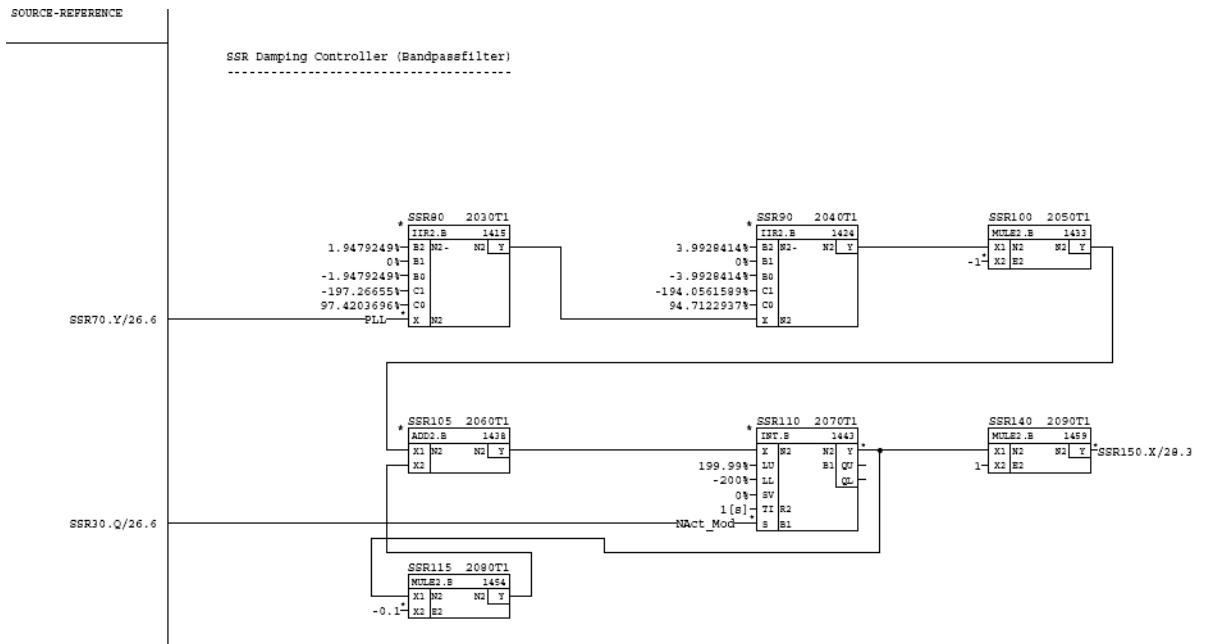

The transfer function of the digital band-pass filter is shown in Equation 1.

$$H_{BP4}(Z) = \frac{d1_0 + d1_1 z + d1_2 z^2}{c1_0 + c1_1 z + c1_2 z^2} \cdot \frac{d1_0 + d1_1 z + d1_2 z^2}{c1_0 + c1_1 z + c1_2 z^2} \quad (1)$$

The parameters of the digital band-pass filter are determined according to the frequency range of sub-synchronous oscillation (Figure 7).

Figure 7. Block diagram of the band-pass filter.

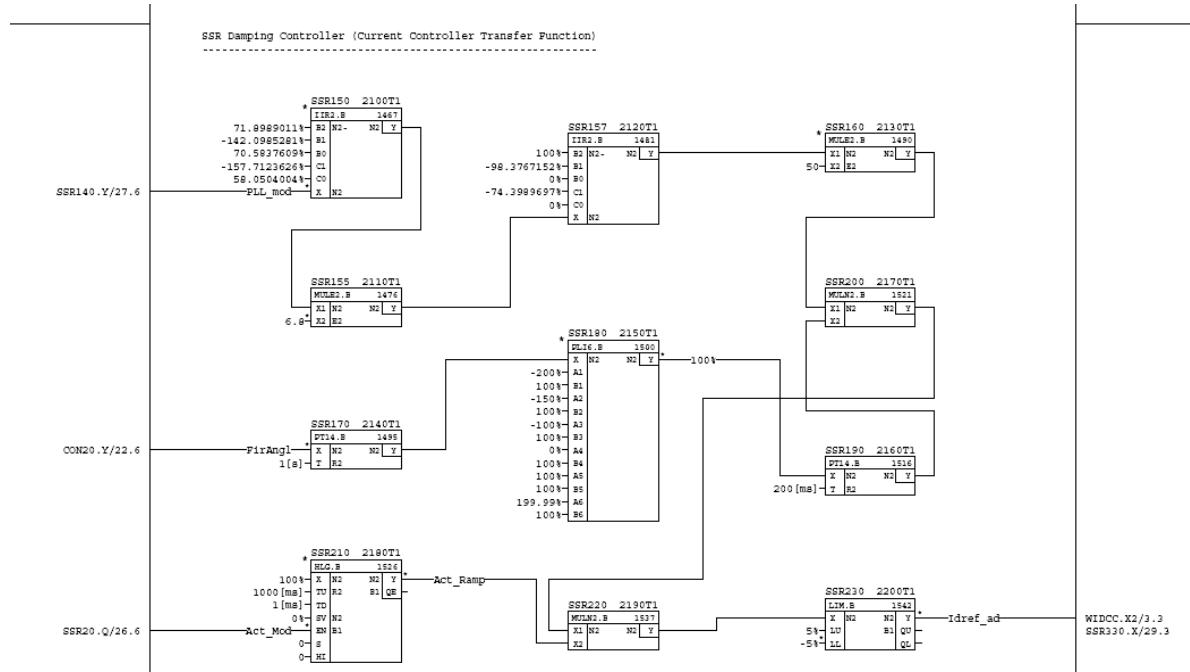

### 3.1.3. Current control stage

The PI control algorithm is employed with a proportional coefficient of 0.9 and an integral time constant of 25 ms. The controller modulates the DC reference value, with an adjustment range of less than 5% of the rated current. The program is shown in Figure 8.

Figure 8. Current control circuit diagram.

### 3.1.4. SSR alarm

The alarm threshold for SSR function output is set at 0.25%, as shown in **Figure 9**.

**Figure 9.** SSR alarm procedure diagram

## 4. Requirements for monitoring indicators of low-frequency inter-harmonics

### 4.1. Frequency band

The actual SSR resonance frequency of the unit in Plant B is 13.34 Hz, 23.83 Hz and 26.77 Hz. Therefore, the frequency band of the harmonic measuring device should be 10–30 Hz, and it should be able to analyze the frequency of the resonance point.

### 4.2. Signal accuracy

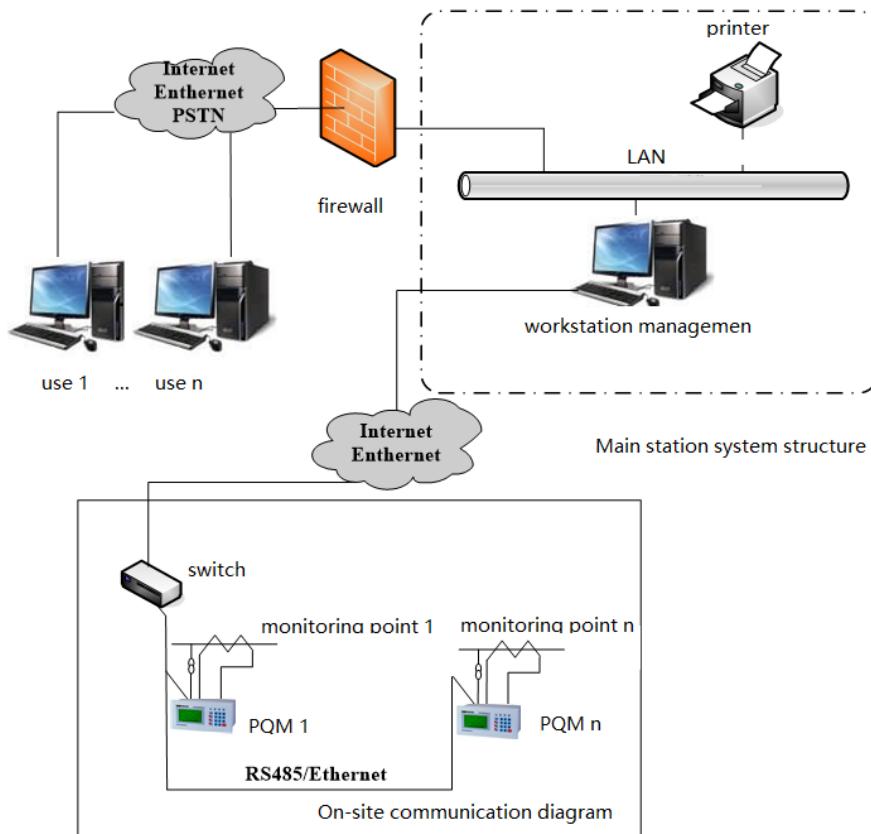

The threshold for SSR alarm in the control system is 0.25%, but when the SSR at converter station A activates, the amplitude of the SSR component is less than 0.2%. Therefore, to achieve accurate measurement, the signal accuracy of the harmonic measurement device must be higher than 0.1%. Therefore, the monitoring system is designed to detect and analyze inter-harmonic signals in the 10–30 Hz range, with alarm triggers for critical points and signal exceedances. It also records event logs to provide data support for addressing sub-synchronous oscillation issues between Converter Station A and Power Plant B. The system's network architecture is illustrated in **Figure 10**.

Figure 10. System network structure diagram.

## 5. Selection and setup of monitoring sites

Based on the actual conditions at the converter station site, 12 monitoring points have been established, with 8 distributed on the AC side of rectifier-inverter units and 4 across the 4 busbars. Each rectifier-inverter unit is equipped with two power quality monitoring devices, totaling 8 units across all 4 units at the station. Additionally, a power quality monitoring panel cabinet (Figure 11) has been installed in the relay protection room, and a complete online power quality monitoring system (including both software and hardware) has been deployed in the main control room to facilitate real-time and historical data access.

### 5.1. AC-side monitoring point of the AC-DC-AC flow unit B

The voltage signals at monitoring points 1, 3, 5, and 7 are obtained from the PTs of the WA-WT1, WA-WT2, WA-WT3, and WA-WT4 units, respectively. As the 500 kV AC bus adopts a 3/2 connection, the current signal is calculated as the sum of the secondary currents from CT3 and CT2 of the bus tie unit, reflecting the actual current at the AC output of the converter substation for harmonic analysis.

### 5.2. AC-DC-AC flow unit A AC-side monitoring point

The voltage signals at monitoring points 2, 4, 6, and 8 are taken from the PTs of units WB-WT1, WB-WT2, WB-WT3, and WB-WT4, respectively. The current signals are similarly obtained by summing the secondary currents of CT1 and CT2 in the bus tie unit.

### 5.3. Busbar monitoring point

The voltage signals at monitoring points 9, 10, 11, and 12 are drawn from the PTs of busbars #1M, #2M, #3M, and #4M, respectively. The current signals are obtained from the line currents of #1, #5, #I, and #II lines, calculated as the sum of the CT currents on both sides of the line nodes.

Figure 11. Schematic diagram of monitoring point selection for converter station.

## 6. Monitoring data configuration

The traditional power quality monitoring device mainly monitors the integer multiplication of inter-harmonic data, and the corresponding configuration adjustment is needed to realize the low-frequency inter-harmonic monitoring.

### 6.1. Addition of a low-frequency data area

A low-frequency data area was added as shown in **Figure 12**.

|               |                                     |                                                                                                                                                                                 |

|---------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0640        | Low-frequency data update indicator | After updating the low-frequency data in DSP, this value is set to the low-frequency data indicator (0..5). After the mainboard reads the low-frequency data, it is set to 0xff |

| 0x0641~0x06A4 | Low-frequency data area             | The first 50short represents the amplitude, while the second 50short represents the phase                                                                                       |

Figure 12. Data block configuration table.

### 6.2. Addition of transient waveform recording trigger criteria

The recording startup configuration table is shown in **Figure 13**.

|        |                             |                                                                                                                                                                                                                                                                                                            |

|--------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1F86 | Transient triggering reason | 0: Exceeding threshold 1: Voltage mutation 2: Manual 3. Starting current 4. Current exceeding threshold 5. Voltage imbalance exceeding 6. Current imbalance exceeding 7. Frequency exceeding limit 8. Frequency under-limit 9. THDU 10. THDI 11. Voltage harmonic exceeding 12. Current harmonic exceeding |

|--------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 13. Recording startup configuration table.

### 6.3. Accuracy correction

The accuracy correction configuration table is shown in **Figure 14**.

|               |                            |                                                                        |

|---------------|----------------------------|------------------------------------------------------------------------|

| 0x0085~0x008A | Accuracy correction factor | They are A-phase voltage, current, B-phase voltage...<br>Unit: 1/10000 |

|---------------|----------------------------|------------------------------------------------------------------------|

**Figure 14.** Accuracy correction configuration table.

### 6.4. Data structure configuration

The data structure configuration is shown in **Table 1**.

**Table 1.** Data structure configuration table

| Data             |           | Position (byte)      | Bytes | Type | Remarks                                                                                                          |

|------------------|-----------|----------------------|-------|------|------------------------------------------------------------------------------------------------------------------|

| Time             | Second    | 0                    | 1     | Char | The time for harmonic recording. The last two digits are the year, and the first two digits are the default year |

|                  | Component |                      | ..    | ..   |                                                                                                                  |

|                  | Time      |                      | ..    | ..   |                                                                                                                  |

|                  | Sun       |                      | ..    | ..   |                                                                                                                  |

|                  | Moon      |                      | ..    | ..   |                                                                                                                  |

|                  | Year      |                      | ..    | ..   |                                                                                                                  |

| Continue to have |           | 6                    | 2     | Char | Keep = 0                                                                                                         |

| A Xiang          | 1 Hz      | Amplitude of voltage | 8     | ..   | ..                                                                                                               |

|                  |           | Phase of voltage     |       |      |                                                                                                                  |

|                  |           | Amplitude of current |       |      |                                                                                                                  |

|                  |           | Current phase        |       |      |                                                                                                                  |

|                  | 50 Hz     | Current phase        |       |      |                                                                                                                  |

| B Xiang          | 1 Hz      | Amplitude of voltage |       | ..   | ..                                                                                                               |

|                  | 50 Hz     | Current phase        |       | ..   | ..                                                                                                               |

| C Xiang          | 1 Hz      | Amplitude of voltage |       | ..   | ..                                                                                                               |

|                  | 50 Hz     | Current phase        |       | ..   | ..                                                                                                               |

### 6.5. Modification of communication protocol

The communication protocol configuration is shown in **Figure 16**.

|                            |                                                                           |                 |    |                                                |

|----------------------------|---------------------------------------------------------------------------|-----------------|----|------------------------------------------------|

| (101)CMD_LOWFREQ_L<br>IMIT | Read/write<br>low-frequency<br>exceeds the limit<br>value(big-endian<br>) | 0               | 1  | Read or write, 0=read, 1=write                 |

|                            |                                                                           | 1               | 2  | 1Hz voltage interharmonic limit factor Unit: % |

|                            |                                                                           | 3               | 2  | 2Hz Voltage interharmonic limit                |

|                            |                                                                           | ..              | .. |                                                |

|                            |                                                                           |                 | 2  | 49Hz Voltage interharmonic limit               |

|                            |                                                                           |                 | 2  | 1Hz Current interharmonic limit                |

|                            |                                                                           |                 | 2  | 2Hz Current interharmonic limit                |

|                            |                                                                           | ..              | .. |                                                |

|                            |                                                                           |                 | 2  | 49Hz Current interharmonic limit               |

|                            |                                                                           |                 |    |                                                |

| (102)CMD_LOWFREQ_R<br>EC   | retrieve<br>low-frequency<br>data                                         | Same as CMD_HRM |    |                                                |

**Figure 16.** Communication protocol configuration table.

## 7. Conclusion

By optimizing the layout and retrofitting of monitoring points in a DC power system, low-frequency inter-harmonics on both sides of the converter transformer, including bus voltage and line current, can be effectively monitored. In practical applications, analyzing the parameters of the DC converter station's damping controller is essential to ensure signal accuracy. The monitoring points and data configurations of the power quality monitoring device are largely consistent, providing accurate and reliable reference data for sub-synchronous oscillation analysis.

## Disclosure statement

The author declares no conflict of interest.

## References

- [1] Wang J, E S, 2009, Causes and Solutions of Sub-Synchronous Oscillation in the Gaoling Converter Station Project. Northeast Electric Power, 2009(11): 20–21.

- [2] Gao B, 2010, Design and Implementation of a Damped Controller for Additional Sub-Synchronous Oscillations in High-Voltage Direct Current Transmission Systems. High Voltage Technology, 36(2): 501–506.

### Publisher's note

Bio-Byword Scientific Publishing remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.