# **OPEN**

# EMI Reduction in Low Input Ripple DC-DC Converter using Chaos PWM technique

Antonella Ragusa, Giuseppe Marsala

National Council of Research, ISSIA UOS di Palermo, Palermo, Italy

**Abstract:** This paper presents a chaotic PWM switching technique for a high boost DC-DC converter with a very low ripple at the input current. The use of a choatic PWM allows a reduction of Electromagnetic In (EMI) at the output of power converters by spreading the energy spectrum of the output voltage. In this paper a chaotic PWM, using the Chua oscillator, has been implemented in Matlab for the converter under study and a comparison with a traditional PWM control has been done. A detailed description of the generation of the chaotic carrier is presented and the effect on the output EMI mitigation has been shown.

**Key words:** EMI; Chaotic PWM; Spreading Spectrum; DC-DC converter

Corresponding author: Antonella Ragusa, E-mail: ragusa@pa.issia.cnr.it; Giuseppe Marsala, E-mail: marsala@pa.issia.cnr.it

## Introduction

The electronic power converters, used in many technology fields, such us automotive, renewable energy, aerospace, etc, are sources of Electromagnetic Interference (EMI) that can cause malfunctions in the electric/electronic devices that share the same electromagnetic environment of the power converters. The switching operation generates high du/dt and di/dt that can cause both conducted and radiated EMI<sup>[1]-[4]</sup>.

For these reasons and in order to comply the limits imposed by the Electromagnetic Compatibility (EMC) standards, EMI reduction techniques have to be adopted; these are passive/active filters, shielding, optimization of layout, random switching techniques<sup>[5]-[10]</sup>.

The use of filters, shielding and techniques of layout optimization have some drawbacks in terms of weight,

volume and cost. Among the reduction methods, the random-switching techniques have been applied in the last decade, resulting the least-cost and effective solutions<sup>[11]-[15]</sup>.

The main idea of these switching techniques is to spread the spectrum of the disturbances such that the power at specific frequencies is reduced to conform the EMI standards without any additional filters. Among these, the chaos technique is employed to switch the converter with chaotic PWM pulses obtaining a spreading of the output disturbances and a reduction of EMI<sup>[15]-[18]</sup>.

A chaotic carrier waveform can be generated by digital or analog circuit<sup>[19]-[20]</sup>. The digital chaotic carrier is more accurate than the analogue one and the modification of its frequency and amplitude is simple by using a digital processor. On the other way, the cost of the digital implementation is higher than analogue one. In the analogue implementation, the chaotic frequency can be modified changing the resistance and the capacitance of the chaotic circuit. Due to the nonideal characteristics of these passive components, the analog chaos carrier waveform is less accurate than digital one and the hardware implementation is more complex.

This paper proposes a chaos PWM switching technique for a high boost low input ripple DC-DC converter designed by the Authors<sup>[21]</sup>. The chaos carrier has been generated employing an analog circuit. In particular, among the chaotic oscillator existing in literature, the Chua's oscillator has been adopted<sup>[22]</sup>. This is a simple circuit that uses only two operational amplifiers that can be easily integrated on a chip. The performance of the DC-DC converter with a Chaotic PWM has been analysed and compared with the performance related to a traditional PWM. In particular, the spreading of the output voltage spectrum has been verified and simulations have been done, using a high frequency (HF) model of the DC- DC converter under study, to validate the effects of the chaotic carrier to reduce EMI.

#### **1 DC-DC Converter under Study**

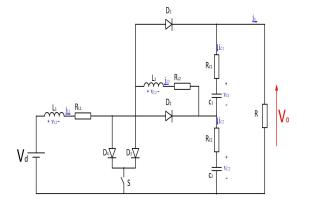

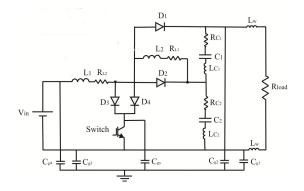

The low input current ripple high boost converter under study is shown in fig. 1. It is a current-fed stepup converter designed to produce an output voltage about four times higher than the input voltage and a low input current ripple. In Continuous Conduction Mode of operation, the state space equations of the converter in ON-state and OFF-state are, respectively:

$$\begin{cases} V_{d} - L_{1} \dot{x}_{1} - R_{L1} x_{1} = 0 \\ L_{2} \dot{x}_{2} + R_{L2} x_{2} - R_{C2} C_{2} \dot{x}_{4} - x_{4} = 0 \\ x_{4} + R_{C2} C_{2} \dot{x}_{4} + x_{3} + R_{C1} C_{1} \dot{x}_{3} + RC_{1} \dot{x}_{3} = 0 \\ C_{1} \dot{x}_{3} = C_{2} \dot{x}_{4} + x_{2} \end{cases}$$

(1.a)

$$\begin{cases} -V_{d} + L_{1}\dot{x_{1}} + R_{L1}x_{1} + R_{C2}C_{2}\dot{x_{4}} + x_{4} = 0 \\ L_{2}\dot{x_{2}} + R_{L2}x_{2} + R_{C1}C_{1}\dot{x_{3}} + x_{3} = 0 \\ -x_{4} - R_{C2}C_{2}\dot{x_{4}} - x_{3} - R_{C1}C_{1}\dot{x_{3}} + Ri_{o} = 0 \\ i_{o} = x_{2} - C_{1}\dot{x_{3}} \\ C_{1}\dot{x_{3}} = C_{2}\dot{x_{4}} + x_{2} - x_{1} \end{cases}$$

(1.b)

where x is the state vector:  $x = [i_{L1} i_{L2} v_{C1} v_{c2}] = [x_1 x_2 x_3 x_4]$ .

The state space averaging state equations are:

$$\begin{cases} \dot{x} = Ax + Bv_d \\ v_o = Cx \end{cases} (2)$$

with  $A = A_1D + A_2(1 - D)$ ,  $B = B_1D + B_2(1 - D)$ , and  $C = C_1D + C_2(1 - D)$ ; Vo is the output voltage, vd is the input voltage and D is the duty cycle<sup>[21]</sup>.

The input ripple current mitigation, introduced by the converter, is shown in Table 1, that shows the

comparison of the ripple generated by this DC-DC converter with the one generated by conventional boost topology.

#### 2 Chaotic PWM Generation

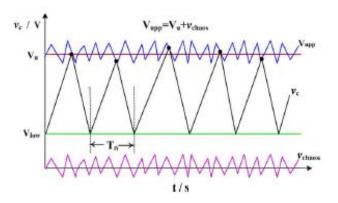

The analogue chaotic PWM, used to switch the DC-DC converter under study, has been generated using the Chua's circuit. The analogue chaotic PWM signal is generated comparing the reference signal with a chaotic triangular carrier, as shown in Figure 2.

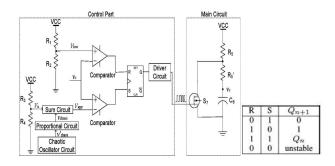

Figure 3. shows the chaotic generator. The chaotic triangular carrier, vc, is obtained by charging and discharging a capacitor, C6, by using a chaotic signal vchaos generated by a chaotic oscillator. The chaotic triangular carrier is generated between a lower limit Vlow, defined by the resistor R1 and R2, and a upper limit Vupp that is the sum of Vu, defined by R3 and R4, and of vchaos<sup>[22]</sup>. When vc is zero, at the start of the devices, or vc< Vlow< Vupp, the input of the R-S flip-flop are R=1 and S=0 that gives an output Qn+1=1. In this condition the switch S7 is ON and the capacitor C6 is charged by VCC. When Vlow <vc < Vupp, R=1 and S=1 and Qn+1=Qn, in this case S7 remains ON until vc reaches Vupp. When R=0 and S=1, Qn+1=0, S7 switches off and the capacitor C6 starts to discharge until vc reaches Vlow. Then, another cycle starts.

The chaotic behavior of Vupp, due to vchaos, makes chaotic vc, with a frequency fn=1/Tn. that varies chaotically around the converter reference frequency, fsw.

Among the well know chaotic oscillators, i.e. Chua's, Lorentz's and Chen's oscillators, in this work the Chua's oscillator is used to generate vchaos voltage.

Fig.1 Low Current Ripple Step-up Converter

Fig.2 Chaotic Triangular Carrier

| Table 1 Comparison | with the Ripple of a | Traditional Boost |

|--------------------|----------------------|-------------------|

|--------------------|----------------------|-------------------|

|    | <i>Ripple</i> $i_{L1}$ % |                  |     |       |                  |  |  |

|----|--------------------------|------------------|-----|-------|------------------|--|--|

| Vo | Boost                    | Low Ripple Boost | Vo  | Boost | Low Ripple Boost |  |  |

| 60 | 2.41                     | 0.92             | 100 | 2.90  | 1.41             |  |  |

| 80 | 2.7                      | 1.22             | 120 | 3.02  | 1.53             |  |  |

Fig.3 Generator of the Chaotic Triangular Carrier

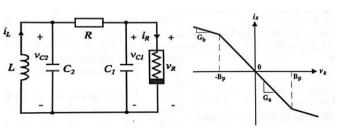

Figure 4. shows a scheme of the Chua's oscillator. The dynamics of the Chua's circuit is described by the following equations:

$$\begin{cases} \frac{dv_{C1}}{dt} = \frac{1}{RC_1} (v_{C2} - v_{C1}) - \frac{1}{C_1} f(v_{C1}) \\ \frac{dv_{C2}}{dt} = \frac{1}{RC_2} (v_{C1} - v_{C2}) + \frac{1}{C_2} i_L \\ \frac{di_L}{dt} = -\frac{1}{L} v_{C2} \end{cases}$$

(3)

where:

$$f(v_C 1) = G_b v_{C1} + \frac{1}{2} (G_a - G_b) (|v_{C1} + B_p| - |v_{C1} - B_p|)$$

(4)

is the vR-iR characteristic of the non-linear resistor of the Chua's circuit. Chua's circuit is a very simple autonomous system that exhibits the complex behavior of bifurcation and chaos. The values of the parameter of the Chua's circuit define the value of the chaotic frequency fn of vchaos. The PWM chaotic signal to switch the DC-DC converter has been

Fig.4 Chua's Circuit and *v-i* Characteristic of the Non Linear Resistor

implemented in Simulink toolbox of Matlab. The Chua's circuit of Figure 4 has been implemented using the differential equation (3) with: R= 1800, C1=10nF, C2=100nF, L=18nH.

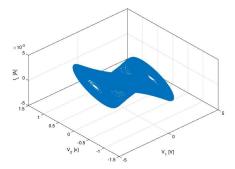

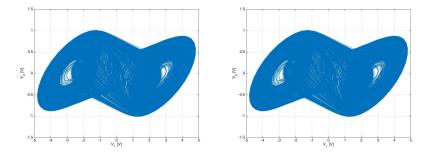

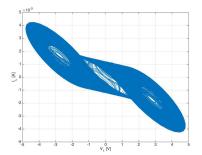

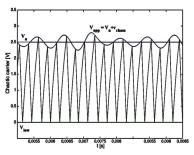

The non-linear resistor defined by relation (3) has been defined by the following values: E=1,17V, Ga=-757, 57 S and Gb=-409,09 S. Wit these values a chaotic frequency, fn that varies chaotically around a reference frequency, fR=10kHz has been obtained. Figs. 5-7 show the obtained chaotic behavior of the waveforms generated by the simulated Chua's circuit. Fig. 8 shows the simulated chaotic carrier voltage, together with the generated Vupp and vchaos. The figure shows that a chaotic frequency around 10 kHz is obtained.

The behavior of the DC-DC converter has been studied using a classic PWM gate signal at a frequency of 10kHz and using the described chaotic PWM gate signal. The effect on the reduction of the harmonics amplitude of the converter output voltage has been studied and the mitigation effects on the output EMI have been verified.

Fig.5 Simulated Chua's Circuit Waveforms

Fig.6 Simulated V2 vs V1 Chua's Circuit Voltages

Fig.7 Simulated IL vs V1 Chua's Circuit Voltages

## 3 Simulations and Analisys of the Results

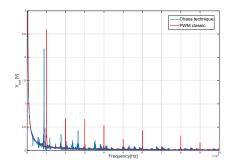

The effects of a chaotic PWM on reducing EMI at the output of the DC-DC converter under study have been studied and verified by Simulation analysis. Tests have been performed by using the Simulink-Matlab software platform, where the DC-DC converter has been modeled, together with the chaotic PWM signal. The advantageous effects of a chaotic PWM are shown in Figure 9. where the Fast Fourier Transform of the output voltage with a classic PWM is compared with the FFT of the output voltage obtained using a Chaotic PWM. Figure 9. shows that a reduction of the harmonic amplitudes is obtained by a spreading the energy spectrum of the output voltage.

As a consequence of the results shown in Figure 9, a reduction of the output EMI of the converter is expected. To verify this effect, a High Frequency (HF) model of the DC-DC converter under study has been

Fig.8 Simulated Chaotic Carrier Waveform

developed and the EMI using a chaotic PWM have been simulated and compared with that obtained using a classical PWM switching signal.

Figure 10. shows the developed HF model of the converter under study. The parasitic inductances of the cable, Lw, the stray capacitances to ground, Cg, of the converter are taken into account<sup>[4]</sup>. Moreover the HF models of the converter output capacitors have been developed<sup>[10]</sup>. The possible values of the considered parasitic elements for the converter under study are shown in Table 2.

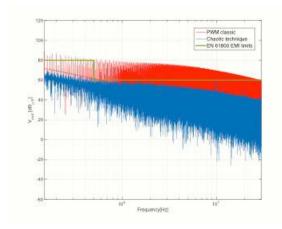

Figure 11. shows the comparison of output EMI of the converter when a classic PWM and chaotic PWM switching signal is used. The Figure reports also the EMI limits defined by the EN 61800 standard. As the figure shows, with a chaotic PWM a reduction of about 20 dBV is obtained and this effect guarantees, also, the respect of the EMI standard limits.

## Fig.9 Comparison of FFT of Vout with Classic Chaotic PWM

Fig.10 HF Model of the DC-DC Converter with Parasitic Parameters

| Parameters                        | Values | Parameters                        | Values |

|-----------------------------------|--------|-----------------------------------|--------|

| C <sub>g1</sub> , C <sub>g2</sub> | 40 pF  | $R_{L1}$                          | 0.4Ω   |

| C <sub>g3</sub> , C <sub>g4</sub> | 30 pF  | R <sub>L2</sub>                   | 0.8Ω   |

| C <sub>gs</sub>                   | 40 pF  | $R_{c1}, R_{C2}$                  | 0.1Ω   |

| L <sub>w</sub>                    | 30 pF  | L <sub>C1</sub> , L <sub>C2</sub> | 30nH   |

Table 2 Possible Values of the Considered Parasitic Elements for the Converter

Fig.1 EMI of DC-DC Converter with Classic and Chaotic PWM, Compared with EN 61800 EMI Limits

## Conclusion

In this paper a chaotic PWM switching technique for a DC-DC high boost converter with very low input ripple isTable 2. Parasitic parameters presented. The chaotic PWM allows obtaining an output EMI mitigation by spreading the output voltage power spectrum. In particular, the Chua's oscillator is used to generate an analog chaotic carrier waveform in Matlab-Simulik environment. A reduction of the harmonic content of the DC-DC converter output voltage has been verified respect to a traditional PWM control. Then, a HF model of the converter under study has been evaluated and the EMI mitigation has been demonstrated. More in detail, the simulation results show that the use of a chaotic PWM allows obtaining an EMI reduction of about 20 dBV.

## References

[1] M. Laour, R. Tahimi, C. Vollaire – "Modeling and Analysis of Conducted and Radiated Emissions Due to Common Mode Current of Buck Converter" – IEEE Trans. on Electromagnetic Compatibility, Vol. 59, No. 4, Aug. 2017.

[2] A. Cataliotti, R. Miceli, D. Di Cara, A. Pecoraro, A. Ragusa, G. Tinè – " Electric and Magnetic Emisison in Near Field Region and Thermal Behaviour of Power Module for Photovoltaic Application" – 4th Inter. Conf. On Renewable Energy Research and Applications, ICRERA 2015, 22-25 Nov. 2015, Palermo, Italy.

[3] G. Marsala, A. Ragusa – "A GA-Neural Network Harmonic Minimization method for Multilevel Inverters with Unequal DC Sources for Different Modulation Index Values" – The 19th Intern. Conf. On Electrical Machines and Systems (ICEMS2016), Nov. 13-16, 2016, Chiba, Japan.

[4] A. Cataliotti, D. Di Cara, G. Marsala, A. Pecoraro,

A. Ragusa – "High-Frequency Experimental Characterization and Modeling of Six Pack IGBTs

Power Modules " – IEEE Trans. On Industrial Electronics Vol. 63, No. 11, Nov. 2016.

[5] Q. liu, S. Connor, C. Olivieri, F. De Paulis, A. Orlandi, M. A. Cracraft, B. Archambeault, V. V. Khilkevich – "Reduction of EMI Due to Common-Mode Currents Using a Surface-Mount EBG-Based Filter " – IEEE Trans. on Electromagnetic Compatibility, Vol. 58, No. 5, Oct 2016.

[6] Y. Chu, S. Wang, Q. Wang – "Modeling and Stability Analysis of Active/Hybrid Common-Mode EMI Filters for DC/DC Power Converters" - EEE Trans. on Power Electronics, Vol. 31, No. 9, pp. 6254-6263, Sept. 2016.

[7] M. Delhommais, G. Dadanema, Y. Avenas, F. Costa, JL. Schanen, C. Vollaire – "Design by Optimization of Power Electronics Converter Including EMC Constraints" – Proc. Of the 2016 Inter. Symposium on Electromagnetic Compatibility – EMC Europe 2016, 5-9 Sept. 2016, Wroclaw, Polland.

[8] G. Marsala, A. Ragusa – "Spread Spectrum in Random PWM DC-DC Converters by PSO&GA Optimized Randomness Level" - The 5th Intern. Symposium on Electromagnetic Compatibility (EMC' Beijing), Beijing, China , Oct. 28-31, 2017.

[9] F. Mihalič, D. kos – "Reduced Conductive EMI in Switched-Mode DC-DC Power Converters Without EMI Filters: PWM Versus Randomized PWM" – IEEE Trans. on Power Electronics, Vol. 21, No. 6, Nov. 2006.

[10] A. Ragusa, P. Zanchetta, L. Empringham, L. De Lillo, M. Degano, "High frequency modelling method of EMI filters for hybrid Si - SiC matrix converters in aerospace applications", 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 17-21 March 2013, Long Beach, CA.

[11] A. Boudouda, N. Boudjerda, B. Nekhoul, K. El khamlichi Drissi, K. Kerroum – "Optimized Dual Randomized PWM Technique for Full Bridge DC- DC converter " – PIERS Proceedings, Marrakesh, Marocco, March 20-23, 2011.

[12] Y.Liu. H. Hong, A. Q. Huang, "Real-Time Calculation of Switching Angles Minimizing THD for Multilevel Inverters whit Step Modulation", IEEE Trans. On Industrial Electronics, Vol. 56, NO. 2, Feb. 2016.

[13] N. Boudjerda, A. Boudouda, M. Melit, B. Nekhoul, K. El khamlichi Drissi, K. Kerroum – "Optimized Dual randomized PWM Technique for Reducing Conducted EMI in DC-AC Converters" -IEEE 2011 Inter. Symposium on Electromagnetic Compatibility - EMC Europe, Sept. 26-30, 2011, York, UK.

[14] G.Marsala, A. Ragusa – "Mitigation of EMI in a Coupled Inductors-High Boost DC-DC Converter by Programmed PWM " - The 5th International Symposium on Electromagnetic Compatibility (EMC' Beijing), Beijing, China , October 28-31, 2017.

[15] H. Li, Z. Li, B. Zhang, F. Wang, N. tan, W. A.

Halang - "Design of Analogue Chaotic PWM for EMI

Suppression " - IEEE Trans. On Electromagnetic

Comp., vol. 52, No.4, Nov. 2010.

[16] H. Li, Y. Liu, T. Zheng, X. Yu, "Suppressing EMI in Power Converters via Chaotic SPWM Control Based on Spectrum Analysis Approach", IEEE Trans. On Industrial Electronics, Vol.61, No.11, Nov 2014.

[17] T. Kapitaniak, Chaos for engineers: theory, applications and control - Springer, Berlin, 1998.

[18] H. Li – Reducing Electromagnetic Interference in DC-DC Converters with Chaos Control – PhD Diss., Hagen Univ., Germany, 2009.

[19] G. Chen, T. Ueta – Chaos in Circuits and Systems – World Scientific Publishing Co. Pte. Ltd., 2002.

[20] R. Mukherjee, S. Nandi, and S. Banerjee, "Reduction in spectral peaks of DC-DC converters using chaos-modulated clock circuits and systems", Proc. ISCAS, vol.4, pp. 3367-3370, May 2005.

[21] G. Marsala, A. Ragusa – Increase of the performance of a low ripple boost converter for PEM FC applications using GA and PSO algorithms - The 8th IEEE Vehicle Power and Propulsion Conference (VPPC 2012) September 9-12, 2012, Seoul, Korea.

[22] P. Galajda, M. Guzan, J. Petrzela, " Implemetation of a custom Chua's diode for chaos generating applications", Radioelektronika, 2016 26th Inter-national Conference, 19-20 April 2016, Slovakia.